摘抄:智能充電器的電源和顯示的設計

第一章 緒 論

充電器才能真正意義上被稱為智能充電器,隨著越來越多的手持式電器的出現,對高性能、小尺寸、輕重量的電池充電器的需求也越來越大。電池技術的持續進步也要求更復雜的充電算法以實現快速、安全地充電,因此,需要對充電過程進行更精確地監控(例如對充(chong)、放(fang)電電流、充(chong)電電壓(ya)、溫度等的監控(kong)),以縮(suo)短充電時間,達(da)到最大的電池容量(liang),并防(fang)止(zhi)電池損壞(huai)。

智能充電器的設計包括硬件和軟件兩大部分,本人的主要任務是完成充電器設計的LCD顯示部分,其主要(yao)涉及的知(zhi)識(shi)包括:

(1) 自學AVR單片機的相關內容。

(2) 設計(ji)電(dian)源電(dian)路。

(3) 設計128*64液晶(jing)顯示(shi)控制電路和(he)用C語(yu)言(yan)編(bian)制LCD顯示(shi)程序,用圖(tu)形方式顯示(shi)充(chong)電(dian)器電(dian)壓、電(dian)流等參數。

(4) 手(shou)工焊接和ICCAVR編譯器(qi)的(de)應用。

第二章(zhang) 硬件電(dian)路設計(ji)

經過前面對充電器原理、液晶模塊、ATmega

通過比較再結合本次設計的實際條件,由于Atmega

2.1 硬件電路主要芯片(pian)

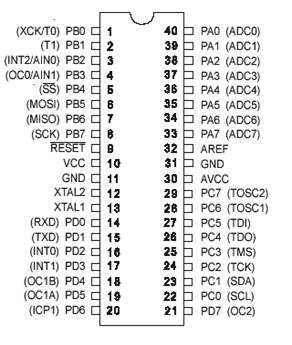

以下(xia)是ATmega

圖2-1 ATmega

引腳說明:

VCC 數(shu)字(zi)電(dian)路的電(dian)源(yuan)

GND 地

端口A(PA7~PA0) 端口A 作為A/D 轉(zhuan)換器(qi)的模擬(ni)輸入端。

端(duan)口A 為8 位雙(shuang)向I/O 口,具有(you)可編程(cheng)的內部上拉電阻。其(qi)輸(shu)出緩沖器具有(you)對稱的驅動特性(xing),可以(yi)輸(shu)出和吸收大電流。

端口B(PB7~PB0) 端口B 為8 位雙向I/O 口,具(ju)有可編程的內部上拉(la)電(dian)(dian)阻。其輸(shu)出(chu)(chu)緩沖器具(ju)有對(dui)稱(cheng)的驅(qu)動特性,可以輸(shu)出(chu)(chu)和吸收大電(dian)(dian)流。

端口C(PC7~PC0) 端口C 為8 位雙向I/O 口,具(ju)(ju)有(you)可編(bian)程(cheng)的(de)內部上拉電阻。其輸(shu)出(chu)(chu)緩沖器具(ju)(ju)有(you)對稱的(de)驅動特性(xing),可以輸(shu)出(chu)(chu)和(he)吸收(shou)大電流。

端口D((PD7~PD0) 端口D 為8 位雙(shuang)向I/O 口(kou),具(ju)有可(ke)編程的內部上拉電阻。其輸出緩沖器(qi)具(ju)有對稱的驅動(dong)特性,可(ke)以輸出和吸收大電流。

![]()

![]() RESET 復(fu)(fu)位輸入引腳(jiao)。持(chi)續時間超過(guo)最小門限時間的(de)低電平將(jiang)引起(qi)系統復(fu)(fu)位。

RESET 復(fu)(fu)位輸入引腳(jiao)。持(chi)續時間超過(guo)最小門限時間的(de)低電平將(jiang)引起(qi)系統復(fu)(fu)位。

XTAL1 反(fan)向振蕩放大(da)器與片內時鐘操作電路的輸(shu)入端。

XTAL2 反向振(zhen)蕩放(fang)大器的(de)輸出(chu)端。

AVCC AVCC是端口A與(yu)A/D轉換(huan)器的電源。不(bu)使用ADC時,該引(yin)腳(jiao)應直接與VCC連(lian)接。使用ADC時應通過一個低通濾波器與VCC相連。

AREF A/D 的模(mo)擬基準輸入引腳(jiao)。

AVR結構有兩個主要的存儲空間:數據存儲器空間和程序存儲器空間,此外,Atmega

(1) Atmega![]() 16的形式。用戶程序的安全性要根據Flash程序存儲器的兩個區:引導(Boot) 程序區和(he)應用程序區,分開來考(kao)慮。

16的形式。用戶程序的安全性要根據Flash程序存儲器的兩個區:引導(Boot) 程序區和(he)應用程序區,分開來考(kao)慮。

(2) 數據存儲器的尋址方式分為5種(zhong):直(zhi)接尋(xun)址(zhi)(zhi)、帶(dai)偏移量的間接尋(xun)址(zhi)(zhi)、間接尋(xun)址(zhi)(zhi)、帶(dai)預(yu)減量的間接尋(xun)址(zhi)(zhi)和帶(dai)后(hou)增量的間接尋(xun)址(zhi)(zhi)。

(3) ATmega

單片機(ji)的時鐘用于產生工作所(suo)需要的時序(xu),其連(lian)接電路如下(xia)圖:

圖2-2 晶體振蕩器連接圖

XTAL1 與XTAL2 分別為用作片內振蕩器的反向放大器的輸入和輸出,考慮到其最大頻率不超過8MHz,這里選用的晶振為7.3728MHz。

Atmega

(1) 上電復位。電源電壓低于上電復位門限Vpot時,MCU復位。如果在單片機加Vcc電壓的同時,保持RESET引腳為低電平,則可延長復位周期。

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() Vcc Vpot Vpot

Vcc Vpot Vpot

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() RESET Vrst Vrst

RESET Vrst Vrst

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() TIME-OUT

TIME-OUT

![]() INTERINAL tTOUT tTOUT

INTERINAL tTOUT tTOUT

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() RESET

RESET

圖2-3 RESET引腳與VCC相連時, 圖2-4 RESET引腳由外部控制時,

單(dan)片機的復(fu)位(wei)電(dian)平(ping) 單片機的復位(wei)電平

(2) 外電復位。引腳RESET上的低電平持續時間大于最小脈沖寬度時MCU復位。

![]() Vcc

Vcc

![]()

![]()

![]()

![]()

![]()