USB Type-C and Rapid Power

For example, USB Type-C alone can support up to 5 volts at 3 amps (15 W), while USB Type-C with USB PD allows the ecosystem to support several power levels up to a maximum of 20 volts at 5 amps (100 W). The downside is that USB PD increases design complexity and the cost of the Bill-of-Materials (BOM).

Fortunately, by using a range of recently introduced components, designers can take advantage of new capabilities such as reversible power delivery, power negotiation and the 100 watt power delivery to design USB power supplies that charge devices – even portable computers – safely and quickly.

This article attempts to cut through the complexity of USB Type-C and USB PD by explaining how designers can use USB Type-C for many applications and when they should migrate to USB PD for higher power applications. The article will then provide guidance on how to implement practical USB Type-C and USB PD designs.

USB gets more focused

Showing a degree of foresight, the original designers of the USB interface decided it should carry both data and power, allowing a low-power peripheral to draw power from the host. Today, billions of electronic devices sport a USB connection and the technology has spread far from its originally intended scope of computer peripherals.

The downside of this remarkable growth was an increase in complexity brought on by a proliferation of connector types, bandwidths, and power levels ranging from the original 5 volts at 100 milliamps up to 20 volts at 5 amps.

Fortunately things are becoming more focused, with new designs tending to opt for the highly-flexible USB Type-C Specification 1.0, 2.0, 3.0, or 3.1 communications protocols; and if higher power is required, USB PD 2.0/3.0 power protocols. This article will consider designs employing these technologies.

USB Type-C and battery charging 1.1 and 1.2

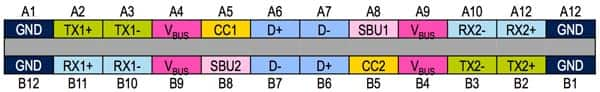

USB Type-C Specification 1.0 was introduced in late 2014 to meet the demand for a compact, reversible plug connector suitable for both host and peripherals for years to come (Figure 1). This future proofing extends to the inclusion of a 24-pin connector which provides four +5 V & ground pairs, two differential pairs for USB 2.0 data bus, four pairs for SuperSpeed data bus, two sideband-use pins, VCONN +5 V power for active cables, and importantly for the scope of this article, channel configuration (CC) pins for cable-orientation detection and management of connections. The pins used in a specific application vary depending on the communication protocol employed and power delivery requirements.

Figure 1: USB Type-C connector pins. CC1 and CC2 are used in the discovery, configuration and management of connections across USB Type-C cable. Note how the pin layout allows reversibility.

As portable devices proliferated it became clear that the 500 mW delivered by the original version of USB would be insufficient to power (and charge) the anticipated range of future portables. Consequently, USB 2.0 introduced a maximum current of 500 mA (increasing the power to 2.5 W) while USB 3.0 pushed the current up to 900 mA (4.5 W).

In another development, the growing capacity of smartphone and tablet batteries, and the fact that USB was increasingly being used for charging, triggered the release of a dedicated battery charging protocol. USB Battery Charging (BC) 1.1, followed by 1.2, was introduced as an engineering change to USB 2.0 in 2010.

The clever part of USB BC was that it recognized that battery charging was an important application for USB. Previously, for example, there was no way of charging the battery of a peripheral device that was switched off. Moreover, even if a device was powered up, if a USB port didn’t receive data from a peripheral for a defined time, it could be set to go into “suspend” mode, allowing a maximum current of just 2.5 mA, far too small for timely battery charging.

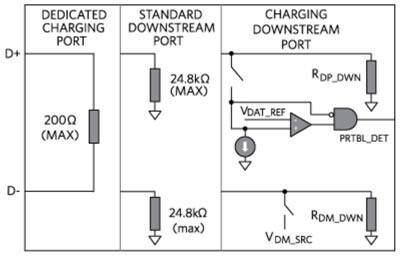

The USB BC spec outlines three distinct types of USB port: A Standard Downstream Port (SDP); a Dedicated Charging Port (DCP); and a Charging Downstream Port (CDP) (Figure 2).

Figure 2: The USB Battery Charging (BC) specification defines three port types, a Standard Downstream Port (SDP), a Dedicated Charging Port (DCP) and a Charging Downstream Port (CDP).

An SDP features 15 kΩ pull-down resistors on both the D+ and D- lines. The current limits are 2.5 mA when “suspended”, 100 mA when connected, and 500 mA when connected and configured for “higher power” (as defined by the USB 2.0 specification). A DCP, as the name suggests, is incapable of supporting any data transfer, but can supply currents up to 1.5 amps for a power delivery of 7.5 watts. In this configuration, the D+ and D- lines are shorted. A CDP allows for both high-current charging and data transfer, being fully compliant with USB 2.0. The port features the 15 kΩ pull-down resistors necessary for D+ and D- communication, and internal circuitry that switches in during the charger detection phase. This internal circuitry allows the portable device to distinguish a CDP from other port types.

All a portable device needs to do to identify a DCP is set a voltage on D+ or D- and observe the other line for that voltage, thus determining that the lines are shorted.

Pushing up the power

USB BC 1.1 did a good job of extending USB’s reach to battery charging and version 1.2 increased output to a maximum of 5 volts at 5 amps (25 W) – sufficient to charge a typical smartphone in around an hour. But designers were further challenged to extend it to products with larger batteries, such as tablets and portable computers.

To meet this demand, the USB Implementers Forum (USB-IF) introduced USB Power Delivery (PD) 1.0 in 2012. A key driver for introducing the standard was to reduce e-waste by offering an interoperable charging standard that would allow manufacturers to offer one charger capable of powering a suite of portable devices.

The key characteristics of USB PD 1.0 include a maximum 20 volts at 5 amps (100 W) (limited by international safety requirements); compatibility with existing USB 2.0/3.0 cables and connectors up to 7.5 watts (otherwise upgraded cables are required); and co-existence with USB BC 1.2.

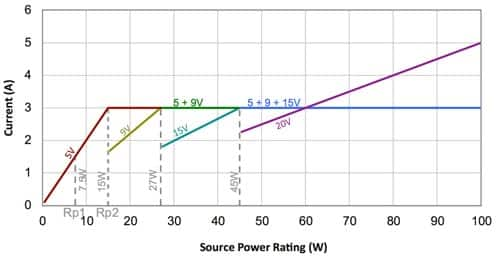

While USB PD 1.0 was capable of providing up to 100 watts, it also provided for several other “Power Profiles”; but these were largely ignored by manufacturers and were removed in USB PD 2.0 and adopted as part of USB 3.1. Now USB PD “Power Rules” replace Power Profiles, defining four voltage levels at 5, 9, 15 and 20 volts. Instead of six fixed levels, power supplies may support any maximum source output power from 0.5 to 100 watts. Sources supplying more than 15 watts offer voltages of 5 and 9 volts, those supplying more than 27 watts offer 5, 9 and 15 volts, and those supplying more than 45 watts offer 5, 9, 15 and 20 volts.

The current can vary continuously (up to 5 A), depending on the required power level. Also, at any given power level, a source is required to support all lower voltages and power levels to ensure that higher-power supplies can support lower-powered devices (Figure 3).

Figure 3: Four voltage levels (5, 9, 15 and 20 V) and currents up to 5 amps are available in USB PD 3.0, enabling power delivery up to 100 watts.

USB PD 3.0 introduced some changes to enhance power delivery and robustness of the system but has made no changes to the Power Rules. USB PD 2.0 and 3.0 are completely interoperable and backwards compatible (Table 1).

|

Table 1: The maximum USB current has increased with the introduction of Battery Charging (BC), Type-C and Power Delivery (PD) Specifications.

For the designer, other notable aspects of the USB PD Specification are the ability of host and peripheral to “negotiate” voltage and current levels using VBUS pins (i.e. without relying on data lines) and the ability to deliver power in either direction without recourse to connector switching. This capability allows, for example, a display connected to mains power to be used to charge a laptop while simultaneously presenting information from the portable computer. Finally, the ability for individual devices to negotiate the exact amount of power they need at any time improves system efficiency.

USB power delivery design

When considering a USB-based design that makes the most of the technology’s power supply capabilities, it’s worth taking a moment to understand how it handles data and power transfer. This has changed considerably from the initial implementation whereby a PC supplied power to a peripheral and data was exchanged both ways.

In today’s implementations, a Downstream Facing Port (DFP) sends data, can source VBUS power and is typically a host or a hub; an Upstream Facing Port (UFP) receives data, sinks (consumes) VBUS power and connects to a host (for example, a display); and a Dual-Role-Data (DRD) port can act as either a DFP or a UFP. In the case of DRD, the port’s role is determined by whether it acts as a power source (DFP) or sink (UFP) at start-up, but its function can be dynamically changed during operation if required. A DRD port is typically used in a smartphone or tablet computer.

When considering power flow, ports can also take on a Dual-Role-Power (DRP) configuration. For example, a portable computer may feature a DRP port that’s used to charge its battery, but may later be used to power an external device such as a hard disk drive. Life gets just a little more complex for the designer here because there are subclasses of a DRP, namely a sourcing device and a sinking host. A sourcing device can supply power, but is unable to act as a DFP. Similarly, a sinking device can receive power, but can’t act as a UFP.

While other USB connectors are still popular, many new designs tend to gravitate towards Type-C because of the long term advantages it offers. Similarly, new designs typically use USB 2.0 or 3.0.

USB Type-C (1.2) without USB PD offers a healthy maximum of 5 volts at 3 amps (15 W), so it is suitable for a wide range of applications without the added complexity of USB PD. For example, 15 watts is sufficient to charge a smartphone battery in 30 minutes or a tablet computer in 2.5 hours. A 5 volt, 1.5 amp (7.5 W) version is also available.

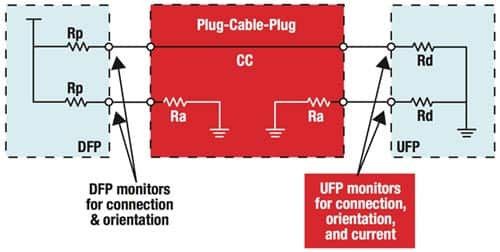

USB Type-C employs pull-up resistors (for a DFP) and pull-down resistors (UFP) on the CC1 and CC2 pins. The pull-up resistor (Rp) determines the DFP’s current provision capacity. A fixed value pull-down resistor (Rd) on the UFP forms a voltage divider with Rp. By sensing the voltage at the center tap of the voltage divider, a UFP can detect a DFP’s advertised current (Figure 4).

Figure 4: Pull-up and pull-down resistors on a DFP and UFP monitor for connection and orientation, while the resistors on a UFP also detect the DFP’s advertised current.

If both ports are DRP capable, the outcome of the connection can be influenced by two optional features: “Try.SRC” (which sets the port as a DFP) and “Try.SNK” (UFP). Such settings can be quite important depending on the application. For example, it would make little sense for a smartphone to start charging a portable computer.

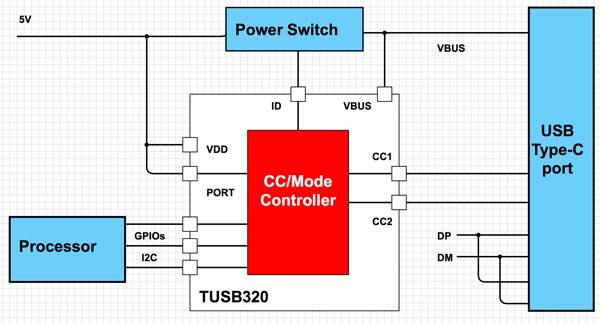

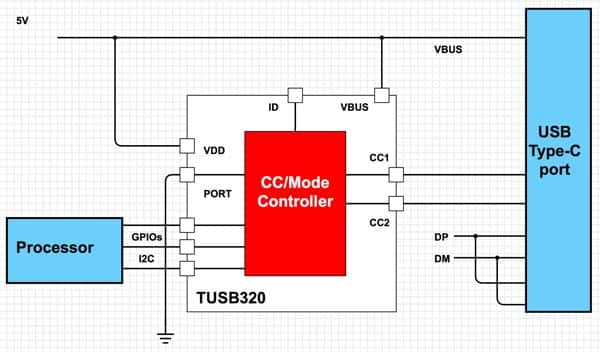

Texas Instruments’ chip is a good basis for a USB Type-C USB 2.0 implementation. It is also a quick way to change a legacy connector USB 2.0 design to a USB Type-C upgrade. An implementation of a DFP using the TI chip is shown in Figure 5. The ID signal indicates a standard on-the-go implementation when the port is configured as a DRP. While it isn’t strictly necessary for a DFP, it comes in handy for controlling the power switch (FET).

Figure 6 shows the UFP implementation with the same chip. This chip can be configured using GPIOs or (optionally) an I2C input and allows for additional designer-friendly functions.

Figure 5

Figure 6

Figures 5 & 6: USB Type-C USB 2.0 DFP (Figure 5) and UFP implementations (Figure 6) using a TI TUSB320 chip.

Adding USB PD

Products that demand more power than can be supplied by a standard USB Type-C port to charge their batteries – such as portable computers – will require the resources of USB PD. The technology allows the peripheral to negotiate for more current and/or higher or lower voltages over the USB cable than are defined in the USB 2.0/3.0/3.1 specifications. Communication is via the USB Type-C CC wire. The downside is that USB PD adds complexity and cost to the design and should therefore only be specified when power support beyond the USB Type-C level of 5 volts at 3 amps is strictly necessary.

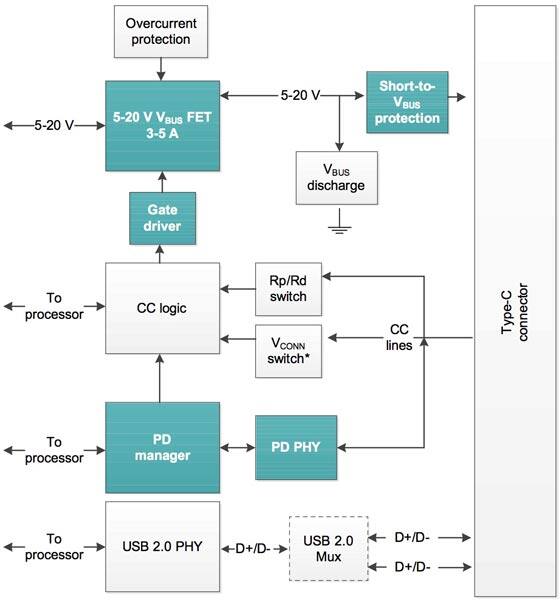

In particular, USB PD requires four new elements compared with the USB Type-C USB 2.0 implementation described above. In addition, the VBUS power switch must be upgraded with a more robust FET to enable it to handle up to 20 volts and 5 amps.

A gate driver is required for the higher power FET. Some designers prefer to use a gate driver that integrates a high-power FET, which can then drive an even higher power external FET. However, because the USB Type-C connector has a higher pin density than legacy USB devices, there’s a higher risk of shorting VBUS to adjacent pins. This is an even more acute hazard when the system is carrying the higher voltages and currents of USB PD.

It’s therefore good design practice to add short-circuit protection to avoid catastrophic failure. Some silicon vendors offer single-chip solutions for this task to save the time involved with designing the protection circuitry.

PD PHY and PD manager

Perhaps the most significant additions to the design when incorporating USB PD are the PD PHY and PD manager. Together, these devices look after the communication across the CC lines between the DFP and UFP. It’s this communication that allows the DFP to advertise what power levels it can support, and then allows the UFP to request a supported power level that meets its needs. Once a power level is agreed upon, voltage and current levels are adjusted. Figure 7 shows the upgraded and added elements required to enable a USB Type-C USB 2.0 design to be capable of USB PD operation.

Figure 7: A USB Type-C USB 2.0 implementation requires the additional highlighted elements (blue blocks) to make it capable of USB PD operation.

The PD manager and PD PHY perform different roles: the PD PHY drives the communication across the CC lines, but in itself it is a “dumb” device. In contrast, the PD manager is an “intelligent” device that consists of a complex state machine that supports the PD negotiation and drives the PD PHY by instructing it to perform functions such as advertising, requesting, and acknowledging power level. The nuances of these functions are complex and beyond the scope of this article. Suffice it to say that USB PD implementations always demand both a PD manager and a PD PHY.

Silicon vendors supply solutions that separate PD manager and PD PHY, or combine both functions onto a single-chip. TI, for example, offers the , a source controller that includes a gate driver for the VBUS power switch, CC logic, USB PD manager and PD PHY. The chip is USB PD 2.0 compliant and so provides for voltages of 5, 12 and 20 volts, and power output from 15 to 100 watts.

The TPS25740 is a suitable foundation for a DFP solution. It automatically handles discharging the VBUS output. Protection features include overvoltage, overcurrent, over-temperature, and system override to disable the gate driver.

Greater integration comes in the form of TI’s . As well as incorporating the USB PD manager and USB PD PHY, the chip controls the external high-current power switch and also multiplexes high-speed data to the port for USB 2.0 and Alternate Mode sideband information. The mixed-signal front end on the CC pins advertises default, 1.5 or 3 amps for USB Type-C power sources, detects a plug event and determines the USB Type-C cable orientation, and autonomously negotiates USB PD power levels. The TPS65982 can operate as a DFP, UFP or DRP.

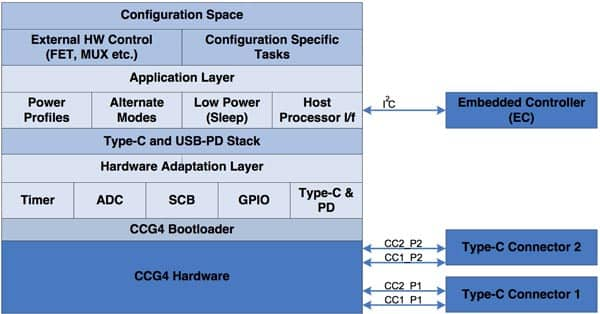

A similarly highly integrated solution comes from with its EZ-PD CCG2 port controller. The chip incorporates an ARM M0 processor with 32 Kbytes of flash and offers not only the USB PD manager and PD PHY, but also integrates a USB Type-C port controller complete with termination resistors. The chip can operate from a 2.7 to 5.5 volt supply and can be used with passive cables, active cables and powered accessories.

Like TI’s TPS65982, the CYPD2103 can be designed into DFP, UFP and DRP topologies and it can also can be modified and configured for a notebook USB Type-C DRP application using the Evaluation Kit. Figure 8 shows the USB Type-C and USB PD specification-compliant firmware stack, along with the application firmware, for the CCG2/3/4 controller that comes with the EVK.

Figure 8: Cypress Semiconductor’s CY4541 Evaluation Kit includes a USB Type-C and USB PD compliant firmware stack.

Conclusion

In parallel to its evolution as a data communication technology offering progressively greater bandwidth, USB technology has evolved to meet the demand for more power handling capability.

In particular, USB Type-C, with its reversible connectors and greater flexibility, along with the USB PD power protocol, offer power levels to meet the demands of portable devices well into the future. This capability is an advantage for developers designing USB power supplies for products that demand high power inputs to reduce charging time.

USB Type-C with USB 2.0 offers a maximum power of 15 watts and bandwidth of 480 Mbit/s. It is suitable for a wide range of applications, is relatively simple to implement and minimizes component costs. For higher power applications, USB PD can be added to new or existing designs, pushing up the maximum power to 100 watts. Designing with USB PD is more complex, but can be eased by basing the power supply around integrated USB Type-C controllers teamed with USB PD PHY/management chips. Note that vendors also offer a range of development tools specifically designed to help engineers accelerate the design process.